IEEE 754의 기본 구조와 정규화/특수값에 대해서 알아본다

부동 소수점의 덧셈과 곱셈의 흐름을 알아본다.

뒤에서 나올 RNE의 의도와 효과를 알아본다

RISC-V에서 기본 부동 소수점 명령이랑 레지스터의 예를 살펴본다

왜 정수가 아니라 ‘부동소수점’인가

컴퓨터는 센서값부터 물리나 금융 계산까지 폭넓은 크기의 실수를 다룬다.

부동소수점은 값을 정규화해서 ±1.~~~ X 2^k 로 표현한다.

아주 작은 수와 아주 큰 수를 같은 형식으로 담을 수 있다.

그리고 정규화를 하게 되면 가수부의 맨 앞에는 항상 1이 존재하는데 굳이 저장하지 않아도 된다.

같은 비트폭에서 유효자릿수를 최대화 하는 것이다.

그리고 부동소수점은 수를 표현할 수 있는 범위가 완전 압도적으로 넓다.

예를 들어 단정밀도는 대략 ±1.0×2^−126에서 ≈±2.0×2^+127까지, 배정밀도는 ±1.0×2^−1022에서 ≈±2.0×2^+1023까지 표현한다.

정수·고정소수점은 같은 비트수로 이만한 동적 범위를 확보하기 어렵다.

마지막으로 특수값으로 예외를 안전하게 처리한다

지수 올 1 & 가수 0 → ±∞(오버플로에 대한 표기),

지수 올 1 & 가수 ≠0 → NaN(정의되지 않은 연산 결과),

지수 올 0 → 서브노멀(0 근처의 완충 구간, 0의 ± 두 표현 포함).

이런 규칙 덕에 계산 도중 오류 체크를 단순화할 수 있다. 그래서 결론적으로 부동소수점은 “정규화된 가수 × 지수” 구조로 정밀도와 표현 범위를 동시에 잡고, 특수값과 표준 규칙으로 수치 계산을 안전하고 일관되게 만든다.

IEEE 754 표준

- S: 1비트, 0=양수,1=음수

- E: 지수 비트, half=5, single=8, double=11

- F: 가수의 소수부 비트, half=10, single=23, double=52

여기서 1+Fraction 부분을 Normalize significant라고 한다.

이 값은 1이상 2미만이다.

그리고 여기서 Fraction에 더해져 있는 1은 항상 있다고 보는 hidden bit이다.

(물론 denormal(subnormal)이라고 해서 히든비트가 0인 상황도 존재한다)

그리고 Exponent-Bias 부분은 다소 의아할 수 있다. (나는 여기가 좀 햇갈렸다)

Exponent-Bias 는 Actual Exponent다.

다시 말해서 수학적으로 ±(1+F)×2e 에서의 2의 지수이다.

Exponent 는 저장되는 지수다. 이 값은 unsigned 로 항상 0이상인 정수다.

Bias 는 E를 만들 때 더해놓는 상수다. Bias의 값은 지수의 비트 개수(k)에 의해서 정해진다.

바이어스를 쓰는 이유는 저장할 지수인 Exponent가 항상 부호 없는 정수로 들고 다녀야한다는 세팅 때문이다.

그러면 Exponent는 왜 저렇게 부호없는 양수가 되어야한다는 세팅이 있을까?

이유는 Exponent의 범위의 양 끝을 특수값으로 예약하기위해서이다.

사실 우리는 숫자 말고 특수값도 표현할 수 있어야한다.(무한대, 0/0, …)

근데 Exponent가 음수가 된다고 한다면 이 값은 2의 보수로 표현해야 할 것이고, 이렇게 표현해서는 특수값을 처리하기 어렵다는 이유가 있다.

특수값

특수값은 E와 F에 의해서 결정되어지는 값들이다.

|

케이스

|

조건(비트 패턴)

|

해석/수식

|

|

서브노멀(denormal)

|

E = 0…0, F ≠ 0

|

히든비트가 0. (x=(−1)S×(0+F)×2,1−Bias). 0 근처를 촘촘히 메움.

|

|

±0

|

E = 0…0, F = 0…0

|

(+0)와 (-0) 두 표현. (x=±0).

|

|

±∞

|

E = 1…1, F = 0…0

|

오버플로우 결과 표기. 이후 계산에 써서 오버플로우 검사 생략 가능. 부호는 S가 결정.

|

|

NaN

|

E = 1…1, F ≠ 0…0

|

정의되지 않는 연산 결과(예: (0/0),(∞−∞)). 값 전파용 표식.

|

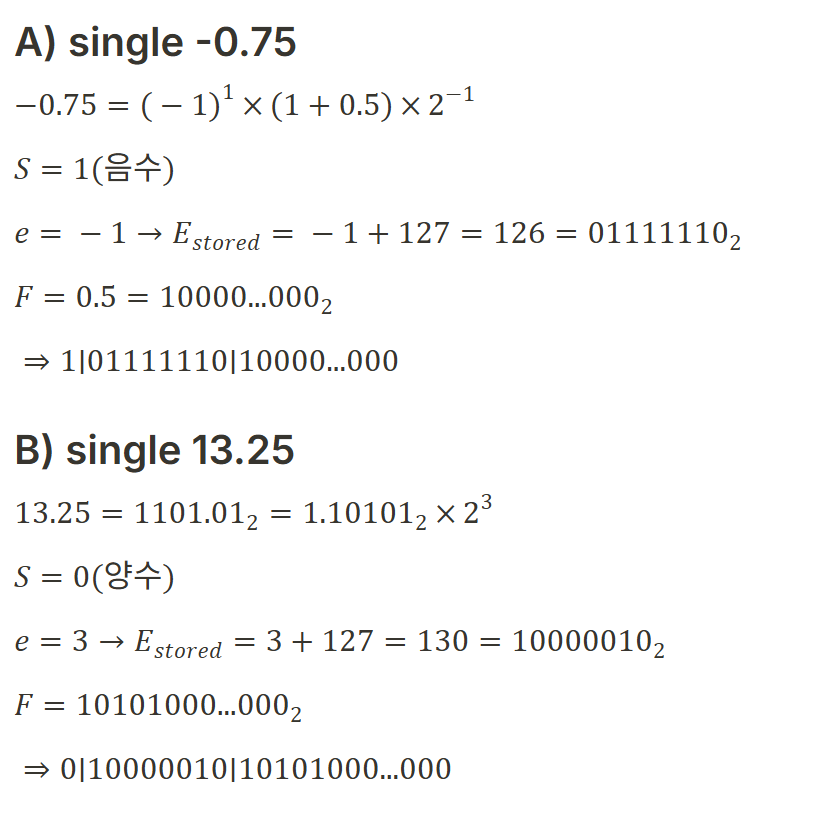

예시

Round to Nearest, Even (RNE)

덧셈/ 곱셈 등 계산 후 정규화된 significant의 유효 비트를 넘어서는 하위 비트를 잘라내며 반올림한다.

라운딩 모드에는 3가지가 있지만 RNE가 가장 기본이고 권장된다.

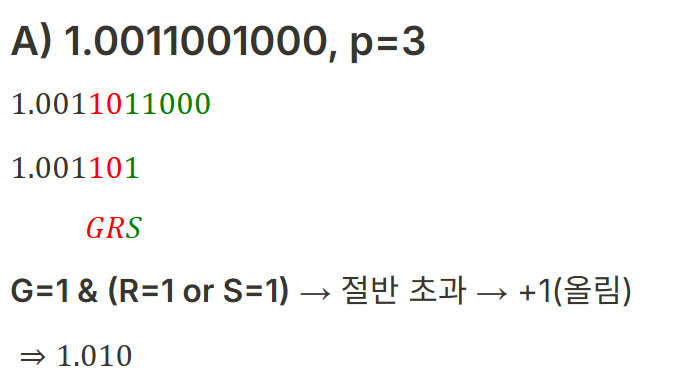

RNE의 핵심은 GRS 비트다

반올림 직전에 보존할 p비트 바로 아래의 3비트를 유지해서 절반 초과/미만/정확히 절반을 판정한다.

cf. 만약 보존할 p비트에 대한 아무 얘기가 없으면 가수 비트 만큼 유지하자

G(guard): 보존부 다음 1비트

R(round): 그 다음 비트

S(sticky): 그 이하 모든 비트를 OR 연산

여기서 규칙을 적용한다.

G=0 → 절반 미만 → 증가 안 함(절사)

G=1 & (R=1 or S=1) → 절반 초과 → +1(올림)

G=1, R=0, S=0 → 정확히 절반 → 짝수 쪽으로 = 현재 보존부의 LSB가 1이면 +1, 0이면 그대로(LSB가 짝수(0)가 되도록 맞춘다.)

예시

Floating-Point Addition

덧셈의 단계는 아래와 같다.

- 정렬: 지수가 작은쪽의 가수를 오른쪽으로 시프트해서 지수를 같게 맞춘다

- 가수 덧셈: 부호를 고려해서 significant를 더한다.(뺄셈도 포함)

- 정규화: 결과를 1.x 로 조정한다.

- 반올림: G/R/S 비트로 RNE 라운딩하고, 필요하면 정규화를 다시 한다.(캐리 발생 이슈)

예시

Floating-Point Multiplication

곱셈의 단계는 아래와 같다.

- 지수 더하기

- 가수 곱하기

- 정규화: 결과를 1.x 로 조정한다.

- 반올림: G/R/S 비트로 RNE 라운딩하고, 필요하면 정규화를 다시한다

- 부호 결정, S=S1⨁S2

예시

'지식 > 컴퓨터아키텍쳐' 카테고리의 다른 글

| Single-Cycle Processor(2) (0) | 2025.10.16 |

|---|---|

| Single-Cycle Processor(1) (0) | 2025.10.16 |

| Arithmetic for Computers(1) (0) | 2025.10.16 |

| Machine Language (0) | 2025.10.16 |

| Instructions(3) (0) | 2025.10.07 |