Architectural State Elements

어떤 저장 요소들이 프로세서의 현재 상태를 결정하는지 알아본다.

CPU의 모든 동작은 이 상태 요소들의 값으로 완전히 결정된다.

|

구성 요소

|

역할

|

크기 / 개수

|

|

Register File

|

연산을 위한 임시 저장소

|

32개 × 32비트

|

|

Program Counter (PC)

|

현재 실행 중인 명령어의 주소

|

32비트

|

|

Memory

|

명령어 및 데이터 저장소

|

보통 수 MB 이상 (32비트 주소 공간)

|

Register File

총 32개의 레지스터가 있다.

각 레지스터는 32비트이고 ALU연산이나 메모리 접근 시 가장 기본적인 저장 단위로 사용된다.

x0은 항상 0으로 고정됨. 규칙임

포트

|

포트

|

방향

|

역할

|

|

A1, A2

|

입력

|

읽을 레지스터의 주소 (rs1, rs2)

|

|

A3

|

입력

|

쓸 레지스터의 주소 (rd)

|

|

RD1, RD2

|

출력

|

읽은 값 (rs1, rs2의 값)

|

|

WD3

|

입력

|

쓸 값 (ALU 결과나 Memory 데이터)

|

|

WE3

|

입력

|

쓰기 제어 신호 (1일 때만 레지스터 갱신)

|

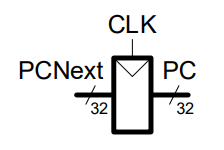

Program Counter

현재 실행 중인 명령어의 주소를 저장하는 32비트 레지스터다

다음 클록마다 다음 명령어의 주소로 갱신된다.

갱신 방식:

- 기본: PCNext = PC + 4 (다음 명령어)

- 분기: PCNext = PC + offset (beq 등 일 때)

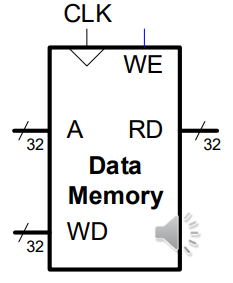

Memory

- Instruction Memory: PC를 주소로 받아서 명령어를 반환

- Data memory: ALU 계산 결과를 주소로 받아 읽기/쓰기 수행

포트

|

포트

|

방향

|

설명

|

|

A

|

입력

|

주소 (Address)

|

|

RD

|

출력

|

읽은 데이터 (Read Data)

|

|

WD

|

입력

|

쓸 데이터 (Write Data)

|

|

WE

|

입력

|

쓰기 제어 신호 (Write Enable)

|

|

CLK

|

입력

|

클록 신호

|

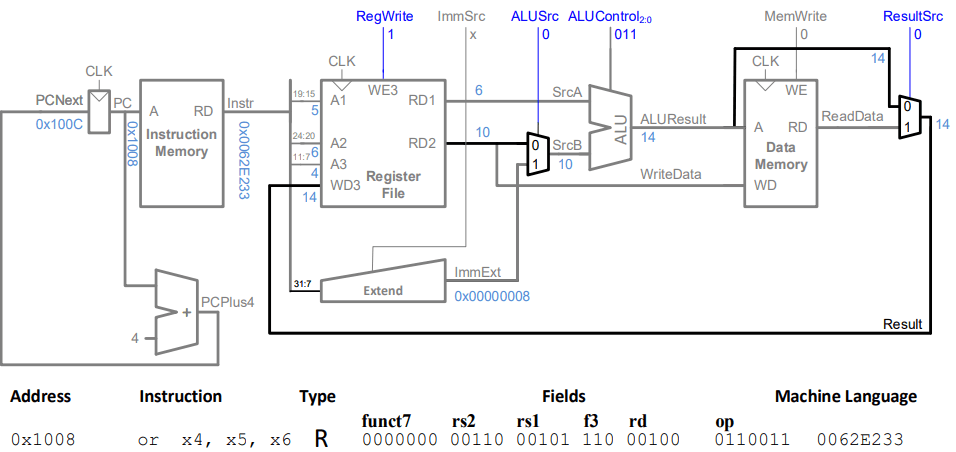

Single-Cycle RISC-V Processor

Single Cycle

싱글 사이클이란 한 명령어가 하나의 클록 주기에서 fetch → decode → execute → memory → write back 단계를 모두 수행한다는 뜻이다.

다시 말하면 , lw, sw, add, beq등 모든 명령어가 한 사이클 안에 완전히 끝난다.

따라서 모든 명령어들의 수행 시간이 똑같다.

하지만 가장 오래 걸리는 명령어에 맞춰 클락 주기를 설정해야되기 때문에 비효율이 발생한다.

Datapath: lw

(1) Program Counter

- 현재 명령어 주소를 보관하는 역할을 한다

- Instruction Memory에 주소를 제공한다.

- 다음 클락에서 PCNext로 갱신된다.

PC → Instruction Memory(2) Instruction Memory

- 입력: PC

- 출력: 32비트 Instruction

- PC가 가리키는 명령어를 읽어서 Register File 등으로 전달하는 역할을 한다.

PC → [Instruction Memory] → Instruction bits (opcode, rs1, rs2, rd, funct3, funct7 등)(3) Register File

- 입력: rs1, rs2, rd

- 출력: RD1, RD2

- 입력 데이터: WD3 (write data)

- 제어 신호: WE3 (write enable)

- ALU나 Data Memory의 값을 읽거나 쓴다.

Instruction[19:15] → A1 → RD1

Instruction[24:20] → A2 → RD2

Instruction[11:7] → A3 ← WD3 (write-back)(4) ALU

- 두 입력 (SrcA, SrcB)

- 하나의 출력 (ALUResult)

- 제어 신호(ALUControl[2:0]

- 수행하는 연산: add, sub, and, or,slt

SrcA = RD1

SrcB = RD2 or Immediate(5) Data Memory

- 주소 입력: ALUResult (계산된 메모리 주소)

- 쓰기 데이터: RD2 (저장할 레지스터 값)

- 출력: RD (read data, load할 데이터)

- 제어 신호: WE (write enable)

ALUResult → 주소

RD2 → WD (write data)

ReadData → Register File(6) PCNext 생성기

- PC+4를 계산해서 다음 명령어 주소로 사용

- Branch 시에는 PC + offset으로 바뀜

- 분기 제어 신호에 따라서 선택되는 것

PCNext = (PCSrc == 0)? (PC + 4) : (PC + Immediate)Single-Cycle Datapath: Other Instructions

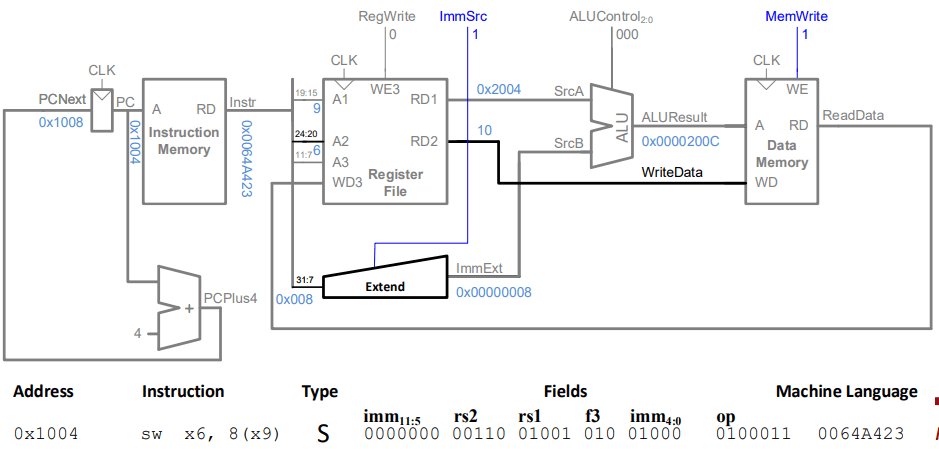

Datapath: sw

sw x6, 8(x9)|

필드

|

의미

|

|

opcode

|

0100011 (S-type)

|

|

funct3

|

010 (word 단위 store)

|

|

rs1

|

x9 (기준 주소)

|

|

rs2

|

x6 (저장할 데이터)

|

|

imm

|

8 (오프셋)

|

⇒ Memory[x9 + 8] ← x6

(1) Instruction fetch

PC가 가리키는 주소에서 명령어를 읽어온다. (sw x6, 8(x9))를 읽어온다.

이 명령어는 Instruction Memory에서 출력되어 Register File과 Immediate Extender로 전달된다.

(2) Register Read

Instruction에서 추출된 rs1과 rs2를 사용해서 두 값을 읽는다.

|

포트

|

읽는 레지스터

|

결과

|

|

A1

|

x9

|

RD1 = x9의 값 (기준 주소)

|

|

A2

|

x6

|

RD2 = x6의 값 (저장할 데이터)

|

(3) Immediate Extend

S-type 명령어는 즉시값이 두 부분으로 쪼개져 있다.

|

비트 구간

|

설명

|

|

instr[31:25]

|

imm[11:5]

|

|

instr[11:7]

|

imm[4:0]

|

따라서 ImmExt는 아래처럼 생성된다.

ImmExt = {{20{instr[31]}}, instr[31:25], instr[11:7]}→ 즉, 이때 제어 신호 ImmSrc = 01 (S-type) 이 선택

(4) ALU

ALU가 주소 계산 수행

ALUResult = RD1 + ImmExt

= x9 + 8(5) Memory write

- ALU 결과가 Data Memory의 주소 입력 A로 전달

- RD2가 Data Memory의 WD로 전달

- MemWrite = 1 일 때만 메모리에 값이 실제로 기록됨

DataMemory[A = ALUResult] ← WD = RD2→ 즉, 메모리의 [x9 + 8] 번지에 x6의 값이 저장됨

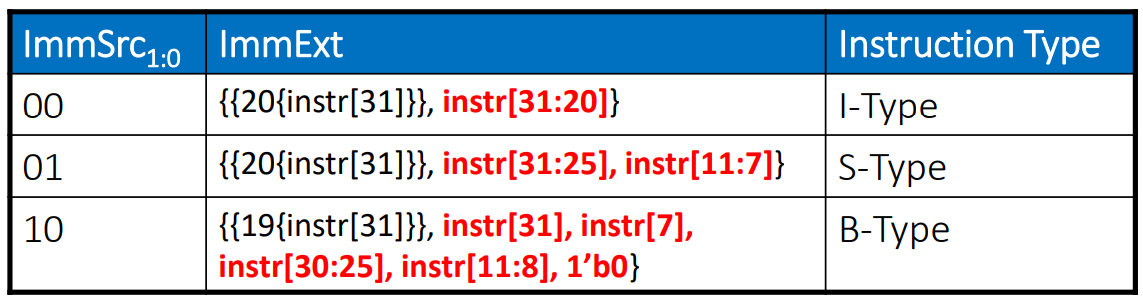

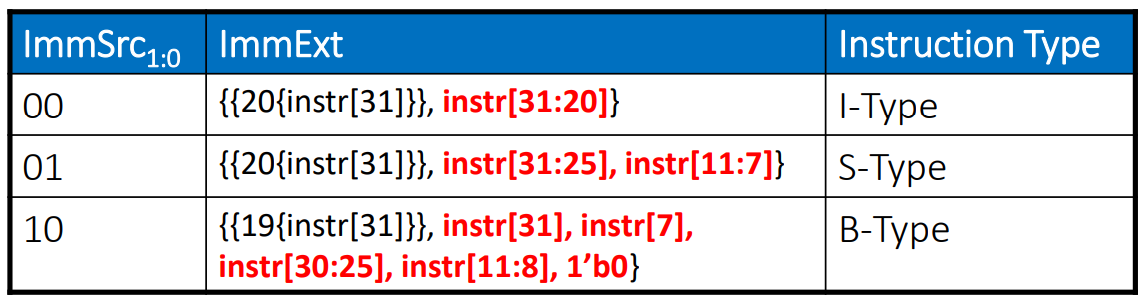

Datapath: Immediate

R-type들은 모두 레지스터 간의 연산이라 즉시값이 필요 없지만

lw, sw, beq 같은 명령어들은 주소 계산이나 분기에 상수 오프셋이 필요함.

그래서 ALU의 두번째 입력은 어떤 명령에서는 레지스터 값(RD2), 어떤 명령에서는 즉시값(ImmExt)를 써야됨

이걸 어떻게 결정하느냐, 제어 유닛은 명령어의 opcode를 보고 결정한다.

Instruction[31:0]

│

▼

┌─────────────┐

│ ImmSrc 제어 │ ← Control Unit에서 opcode 기반

└──────┬──────┘

▼

┌────────────────────────────┐

│ Immediate Extension Block │

│ (Sign-Extend + Bit Select) │

└────────────────────────────┘

│

▼

ImmExt (32-bit)

│

▼

ALU SrcB ← (ALUSrc = 1일 때)Datapath: R-type

R-type은 두 레지스터의 값을 읽어 ALU로 연산한 뒤, 결과를 다른 레지스터에 저장한다.

or x4, x5, x6(1) Instruction fetch

PC가 가리키는 주소에 명령어를 읽는다.

Instruction Memory가 출력한 32비트 명령어는 Register File과 Control Unit으로 전달한다.

(2) Register Read

Register File이 두 개의 레지스터를 읽는다.

|

입력 포트

|

주소

|

출력 데이터

|

의미

|

|

A1

|

instr[19:15]

|

RD1 = x5

|

첫 번째 피연산자

|

|

A2

|

instr[24:20]

|

RD2 = x6

|

두 번째 피연산자

|

(3) ALU

컨트롤 유닛이 func3, func7, opcode를 보고 ALUControl의 값을 결정한다.

funct3 = 110 → OR

funct7 = 0000000

⇒ ALUControl = 011 (OR)

그 다음에 ALU가 연산을 수행한다.

ALUResult = RD1 OR RD2 = x5 OR x6(4) write back

ALU의 결과를 Register File의 rd 에 저장한다.

컨트롤 유닛이 RegWrite=1 로 설정해 쓰기를 활성화한다.

|

입력 포트

|

신호

|

설명

|

|

A3

|

instr[11:7]

|

쓰기 레지스터 주소 (x4)

|

|

WD3

|

ALUResult

|

쓸 데이터 (x5 OR x6)

|

|

WE3

|

1

|

쓰기 허용

|

PC → Instruction Memory → Instruction

│

▼

┌──────────────┐

│ Register File│

│ RD1 (x5) │────┐

│ RD2 (x6) │──┐ │

│ A3 = x4 │ │ │

└──────────────┘ │ │

▼ ▼

┌────────┐

│ ALU │

│ OR │

└────────┘

│

▼

ALUResult

│

▼

Register File (WD3 = ALUResult)Datapath: beq

beq x4, x4, L7B-type 명령어는 아래처럼 즉시값 비트들이 분리되어있다.

그래서 ImmExt 생성 블럭에서 ImmSrc = 10으로 처리했었음

|

비트 구간

|

의미

|

|

instr[31]

|

imm[12]

|

|

instr[7]

|

imm[11]

|

|

instr[30:25]

|

imm[10:5]

|

|

instr[11:8]

|

imm[4:1]

|

|

마지막 비트(imm[0])

|

항상 0 (2의 배수 정렬)

|

ImmExt = sign-extend({instr[31], instr[7], instr[30:25], instr[11:8], 1’b0})

(1) Instruction fetch

PC가 가리키는 주소에서 명령어를 읽어온다. (beq x4, x4, L7)

Instruction Memory →Register File, Immediate Generator

(2) Register Read

Register File에서 두 레지스터를 읽는다

|

포트

|

읽는 레지스터

|

출력 데이터

|

역할

|

|

A1

|

x4

|

RD1

|

비교 대상 1

|

|

A2

|

x4

|

RD2

|

비교 대상 2

|

(3) ALU

ALU가 RD1 - RD2 연산을 수행함

결과로 ALU의 내부 신호 Zero가 만들어짐.

|

신호

|

값

|

의미

|

|

ALUControl

|

001

|

subtract

|

|

Zero

|

1

|

RD1 == RD2일 때

|

|

Zero

|

0

|

RD1 ≠ RD2일 때

|

(4) 분기 주소 계산

동시에 ALU 옆에서 덧셈기가 PC+ImmExt를 계산한다.

PCTarget = PC + ImmExt분기할 때 점프할 주소

(5) PC 선택기

이제 두 개 중에서 하나를 선택해야됨

|

후보

|

의미

|

선택 조건

|

|

PC + 4

|

다음 명령어

|

조건 불일치

|

|

PC + ImmExt

|

분기 대상

|

조건 일치 (Zero=1)

|

컨트롤 유닛이 이걸 결정하는 신호를 생성해줌

PCSrc = (Zero == 1) ? 1 : 0그 다음에 PCNext가 결정됨

PCNext = (PCSrc == 1) ? PCTarget : (PC + 4)(6) PC 업데이트

다음 클락 상승에서 PC가 계산된 PcNext 값으로 갱신됨

PC ───▶ Instruction Memory

│

│ ┌──────────────┐

│ │ Register File│

│ │ RD1 (x4) │───┐

│ │ RD2 (x4) │──┐│

│ └──────────────┘ ││

│ ▼▼

│ ┌────────┐

│ │ ALU │ subtract

│ └────────┘

│ │

│ Zero ─┘

│

│ PC + 4 ─────┐

│ ▼

│ ┌─────────────┐

│ │ MUX(PCSrc)│◀── Zero

│ └─────────────┘

│ ▲

│ PC + ImmExt ┘

│

└──▶ PCNext (선택 결과)'지식 > 컴퓨터아키텍쳐' 카테고리의 다른 글

| Single-Cycle Processor(2) (0) | 2025.10.16 |

|---|---|

| Arithmetic for Computers(2) (0) | 2025.10.16 |

| Arithmetic for Computers(1) (0) | 2025.10.16 |

| Machine Language (0) | 2025.10.16 |

| Instructions(3) (0) | 2025.10.07 |